|

|

|

www.design-reuse-china.com

www.design-reuse-china.com |

|

2nm之战全面打响!背面供电成制胜关键?

毫无疑问,目前台积电赢得了FinFET的战争。所有值得关注的前沿逻辑设计,甚至英特尔的设计,都是在台积电位于中国台湾南部的N5和N3工艺上制造的,竞争对手已被甩在后面。三星自7nm工艺以来性能一直表现不佳,且产量低下;英特尔4nm和3nm工艺仍处于复苏初期;无论是外部客户还是内部客户,都没有大批量订购这些节点的产品。

www.laoyaoba.com/, Oct. 11, 2024 –

但台积电未来能否占据主导地位尚未可知。FinFET无法进一步扩展,而SRAM的微缩在几个节点上已经停滞。该行业正处于关键的转折点。在未来2~3年内,前沿逻辑设计必须采用两种新模式:全环绕栅极(GAA)和背面供电网络(BSPDN或backside power delivery network)。

英特尔在其10nm节点上一败涂地,失去了3年的领先优势,原因有很多,包括没有采用EUV光刻技术,以及在设备供应链不成熟的情况下过渡到钴金属化,尽管应用材料公司警告说他们的设备还没有准备好。GAA和BSPDN的新模式为代工厂的竞争顺序带来了新的机遇。他们甚至有可能为新进入者打开大门,比如日本政府支持的2nm晶圆代工初创公司Rapidus。

随着建造尖端晶圆厂所需的资本支出激增,这意味着三星或英特尔可能被迫退出竞争。下面我们将详细讨论这些话题:深入探讨BSPDN技术,然后介绍所有四家代工厂的前沿逻辑计划、其工艺技术的竞争力以及SRAM的缩放。

GAA并非新技术。根据三星的说法,它已经大批量生产了几年,但实际情况是,它只用于单个低容量比特币挖矿芯片,没有用于任何SRAM和小于20mm²的手表芯片。考虑到本世纪末,从2nm到更先进技术,所有前沿节点都将使用GAA架构,因此该架构是一个重要话题。

背面供电网络是什么?

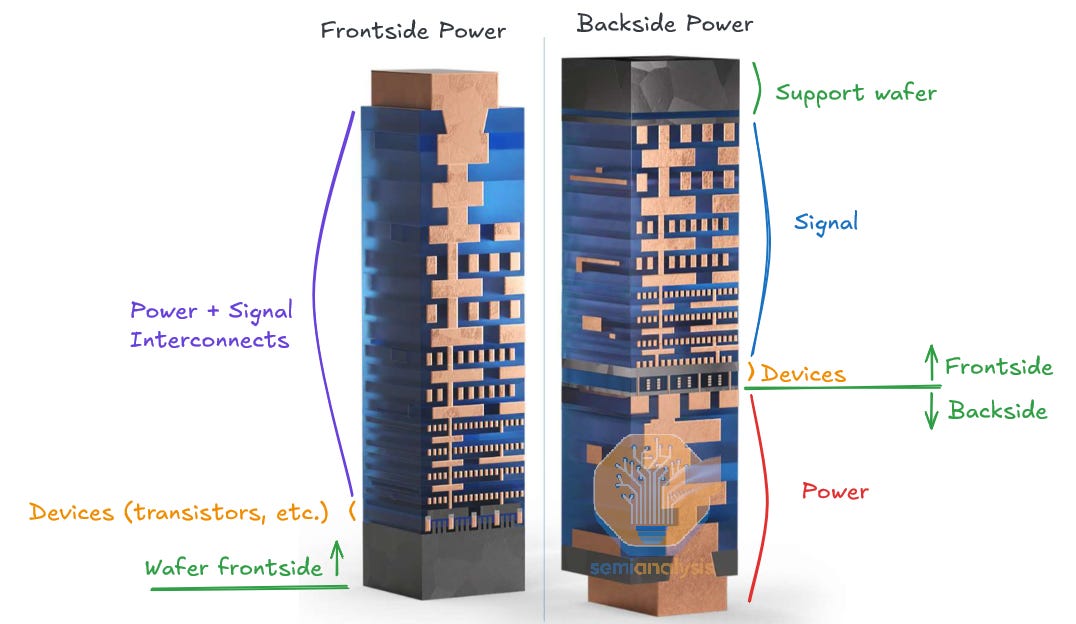

除了GAA晶体管,BSPDN是下一代逻辑工艺技术的另一项关键创新。在目前所有的数字逻辑工艺技术中,首先要在晶圆上制造晶体管,然后再制造数十层金属层,这些金属层为晶体管供电,并在晶体管与外界之间传输信号。

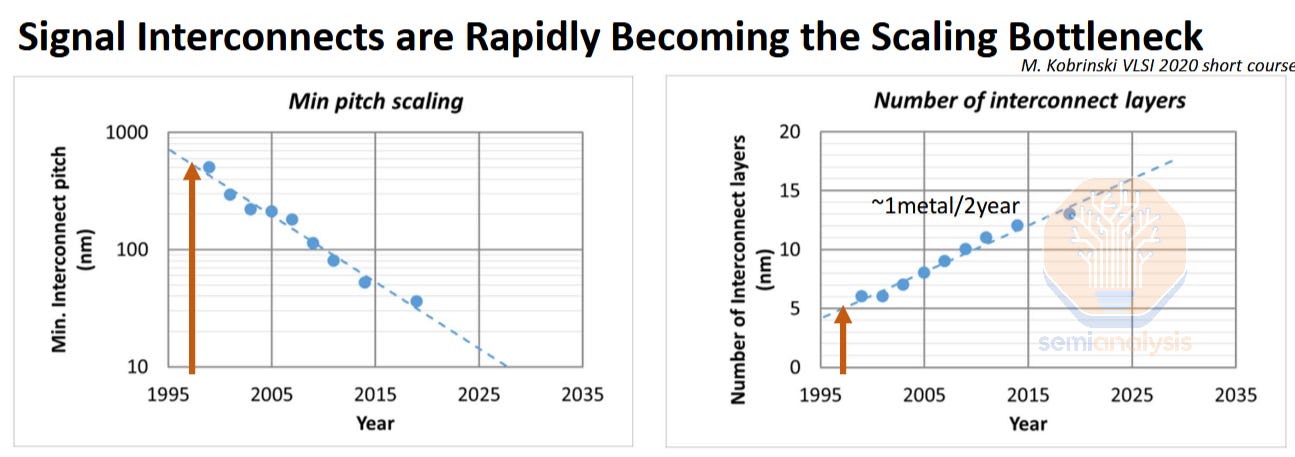

电路的缩小意味着晶体管和互连都必须缩小。在过去,这几乎是一个事后考虑的问题,但现在缩放互连变得比缩放晶体管更加困难。例如,大多数EUV光刻实际上用于互连(触点、通孔和金属层),而不是晶体管层本身。除了导线本身的物理尺寸缩小,芯片上更多的晶体管意味着更多的互连。这推动了所需互连层数的稳步增长。层数越多,意味着制造成本越高,布线设计越困难,并且随着信号路径变长,性能会降低。

来源:英特尔IEDM2023

这并不意味着该行业停止了进步。材料创新、设计技术协同优化(DTCO)和EUV光刻技术推动了互连微缩至当前的工艺节点。但是,随着这种策略变得越来越昂贵,限制也在不断扩大。实施BSPDN开始变得有意义。这并不是什么新想法,只是时机已到。自上次互连技术演变––1997年从铝到铜的转变以来,已经过去了近30年。

资料来源:英特尔,SemiAnalysis

点击阅读更多

Back

Back